[心得] R-2R DAC 電阻精度匹配與模擬

圖文易讀版

http://chihhanlin.weebly.com/r2r-dac-38651384592130537197.html

想搞 audio 的 R-2R DAC? 想學啊? 我教你

http://chihhanlin.weebly.com/uploads/8/4/4/0/8440048/learn_orig.jpg

一樣先寫結論:

R2R DAC 硬體有三寶: 開關, 參考電源和電阻匹配. 這篇文章用靜態電阻匹配計算來模擬

動態可能碰到的失真問題, 擴充一下結合 Re-sorting 跟 Laser trimming (管它開關導

通電阻有多大我連它一起算進 R-2R 修整)的技術應該有機會找出兼具低成本與高效能的

audio R-2R ladder 量產製程.

最後我寫了一個 R-2R DAC 電阻精度匹配與 THD (Total Harmonic Distorsion)的模擬程

式, 稍微動了點手腳(商業機密)讓部份類型的小訊號模擬不是那麼準確, 不過足以佐證

一些量測結果與原理. 這玩意甚至可以做成 R-2R 失真效果器來製造一些測試聽感的

wav 檔.

模擬結果:

陽春架構 0.01% 精度電阻 R-2R ladder 的合理長度是 16-17 bit, THD 了不起達到

-90 至 -100dB

Signed Magnitude / balanced dac 賦予超過合理長度的 R-2R ladder 更多功能, 比如

說小訊號下的 THD 表現

推薦參考資料:

US patent, US5257027, A Modified sign-magnitude DAC and method

http://www.google.com.af/patents/US5257027

2N3904blog -R2R DAC – DC Simulation

https://2n3904blog.com/r2r-dac-dc-simulation

D. Marche, Y. Savaria, "Modeling R-2R segmented-ladder DACs", IEEE Trans.

Circuits Syst. I Reg. Papers, vol. 57, no. 1, pp. 31-43, Jan. 2010

http://ieeexplore.ieee.org/abstract/document/4806048/

Walt Kester, The Data Conversion Handbook

http://www.analog.com/en/education/education-library/data-conversion-handbook

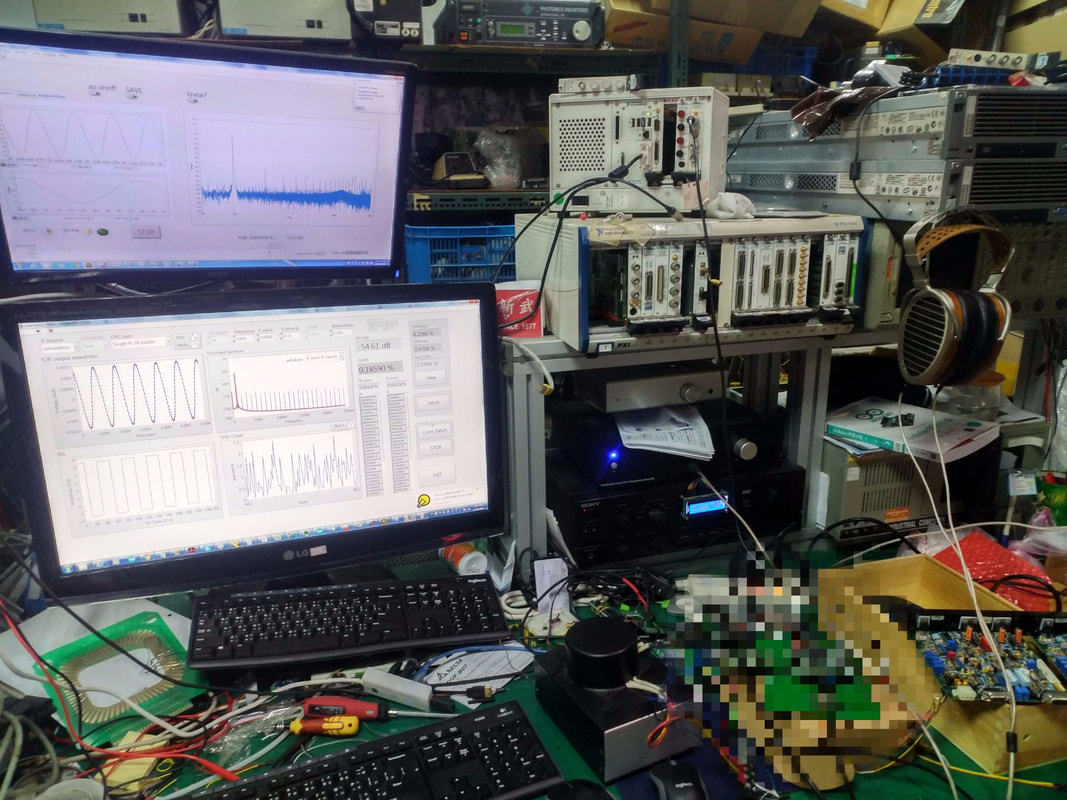

模擬歸模擬, 實際的東西做下去比對才知道模擬有沒有參考價值 . 個人是覺得有那麼點

用處, 多讀點書還是不錯的

http://chihhanlin.weebly.com/uploads/8/4/4/0/8440048/r2rmes_orig.jpg

那一整坨打馬賽克的東東就是測試的樣品, 有NDA所以不能隨便公佈, 右邊看起來很酷炫

板子是 16-bit 雷射振鏡的驅動電路, 跟 audio 完全無關, 不過價格隨便都屌打中階

audio dac.

http://chihhanlin.weebly.com/uploads/8/4/4/0/8440048/r2r_simu_171219.zip

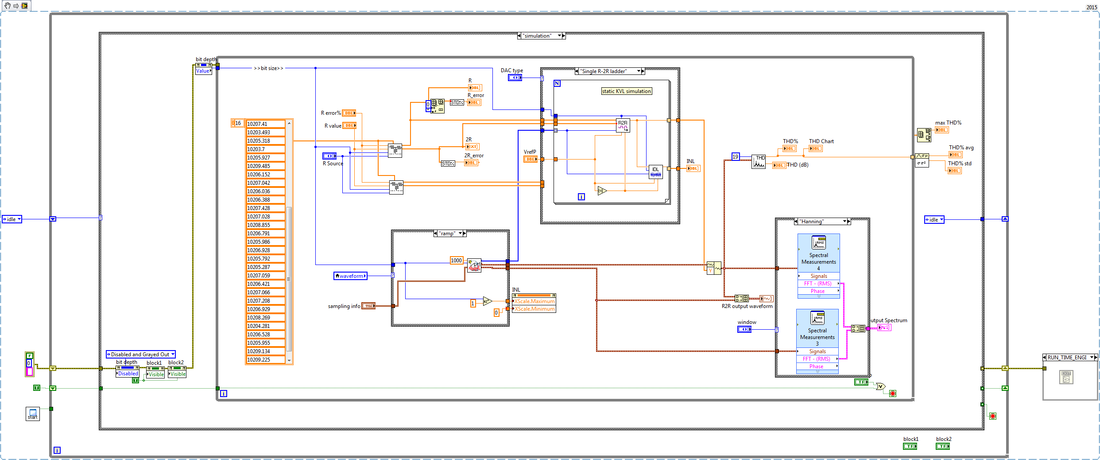

上述壓縮檔就是 demo , 點開 R2R simulator.exe 即可執行, 模擬程式本身不大, 不過

因為是用 LabVIEW 寫的所以執行它需要先安裝官方的 LabVIEW Run-Time Engine 2015

- (32-bit). (這是免費的, 跟 Java 類似也差不多肥大, 200MB-300MB)

http://www.ni.com/download/labview-run-time-engine-2015/5507/en/

---------後記----------

http://chihhanlin.weebly.com/uploads/8/4/4/0/8440048/krab_1_orig.jpg

上個月跑去看香格里拉內構的時候順便在巴城品嘗了正宗陽澄湖大閘蟹, 即便致癌超標還

是值得一吃啊. 下半年一下班就泡在健身房跟家裡的練習台玩 zwift 沒空寫雜文 , 今年

目標就是要蹲破 120kg 5rm , FTP 200W 跟弄出個可以聽的 R2R prototype 啊

-------------本文開始-------------------------

最近開始把 R2R dac 當成比較正式的 side project 來做, 第一步當然要先建立一些有

參考價值的模擬工具, 特別是 R-2R ladder 電阻精度匹配與諧波失真(harmonic

distorsion)的關聯性. 靜態的 DC 分析並不是很困難, 大一電路學教過的 KCL &KVL 配

合一些迴圈就可以快速計算任意 n-bit R-2R 在不同 input code下輸出的類比電壓值,

透過偉大的 google 回顧文獻的時候發現 2N3904Blog 已經幫我們算好了(連 matlab 範

例都寫好了揪甘心), 核心的計算區塊建好用 LabVIEW 快速拉一下就得到不錯的模擬結果

. 雖然模擬中完全忽略掉時域同步以及開關的 glitch 問題, 但對於分立原件的 audio

R-2R dac 設計中究竟需要做到多高的電阻精度匹配才能達到預期的 THD 設計 (當然跟一

般的 sigma-delta 完全不能比, 不過 R2R 互比就靠這個展現技術力)

http://chihhanlin.weebly.com/uploads/8/4/4/0/8440048/main01_2_orig.png

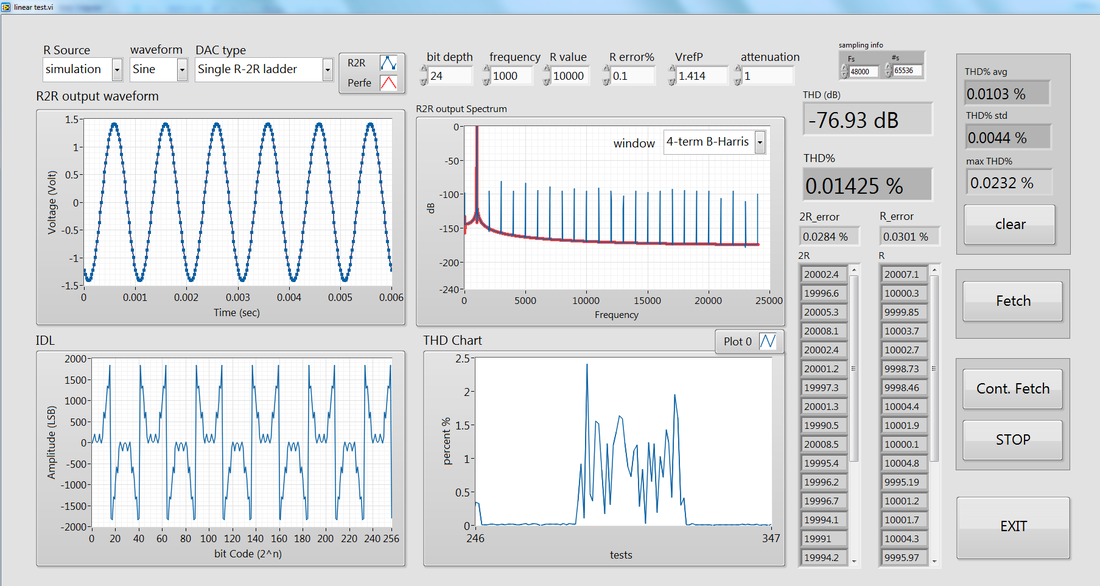

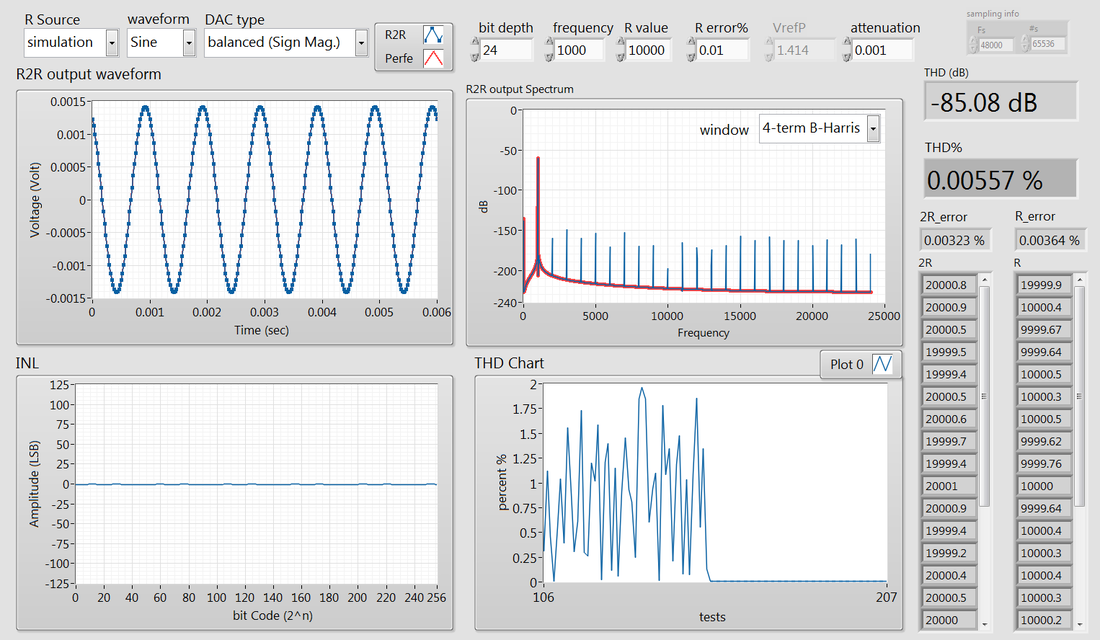

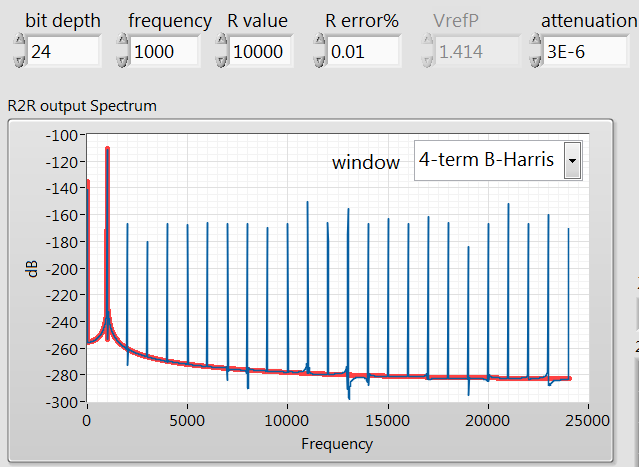

這個程式上方的 R2R output waveform/Spectrum 就是模擬經過實際 R-2R ladder (對應

的實際值在右方的 2R, R 陣列, 2R_error/R_error 為陣列標準差)後得到的類比電壓輸

出, 用大家習慣的 48KHz 取樣率生成 65536 點後丟去做 FFT 看頻譜. 紅線就是理想輸

出, 藍線則是電阻值 mismatch 的 R2R 產生的失真波形. 下方的 IDL (integral

Nonlinearity) 指的就是實際輸出值與理想值的差距, 以上圖來說就是 24bit 的普通

R2R 電阻匹配 0.1% 的時候, 單電壓的絕對誤差最高可能有 2000 個 bits (LSB), 換

句話說幾乎 2^11 ~ LSB 側的 11bit 在 Full range 的時候(0dBFS)幾乎都是沒有意義

的, 有效位數頂多 24-11=13bit, 這也就是絕大多數晶圓製程的工業用 R-2R 類型的

dac 晶片當中 R-2R ladder 通常只做 10-14 層的原因, 它們應用上都需要極低的

INL (就像一把刻度等距均勻的尺).

HiFi 領域分立/離散元件構成的 R-2R dac 架構幾乎都是電壓型 (類似 AD5791 , 可參考

從拆機談起 http://chihhanlin.weebly.com/2447825286272313552736215.html

完整的等效電路分析個人推薦看這篇 D. Marche, Y. Savaria, "Modeling R-2R

segmented-ladder DACs", IEEE Trans. Circuits Syst. I Reg. Papers, vol. 57,

no. 1, pp. 31-43, Jan. 2010, 裡面也分析了幾種 Segmented-ladder 變體 (這個在

我之前的文章稱作 Hybrid R2R, 看了一些 paper 發現 Segmented 這個字眼比較常用,

總之就是 MSBs 端採用 string/多電阻並聯的架構來克服 binary weighting 的電阻網路

匹配問題, 可以在維持同樣的 DNL/INL 下再提昇 3-6 bit 的有效位數 ). 電壓型

R-2R 的優點在於輸出阻抗恆定, 但是輸入阻抗變化大所以很吃參考電壓源, 與主流的

delta-sigma DAC 相比在動態範圍以及 out-of -band noise 會有比較大的優勢, 聽感

上非常討喜, 雖然現階段還沒研究出箇中原因 (目前只有模擬過一種 double-chirp 的

信號從動態頻譜上可以觀察到一些明顯的差異, 不過也不算正規的測試就先不談). 另外

各位對於 AD/DA 有興趣的話建議各位可以翻一下 Walt Kester 寫的 The Data

Conversion Handbook, 在 AD 網站的 Education Library 裡可以找到, 是很棒的入門教

材.

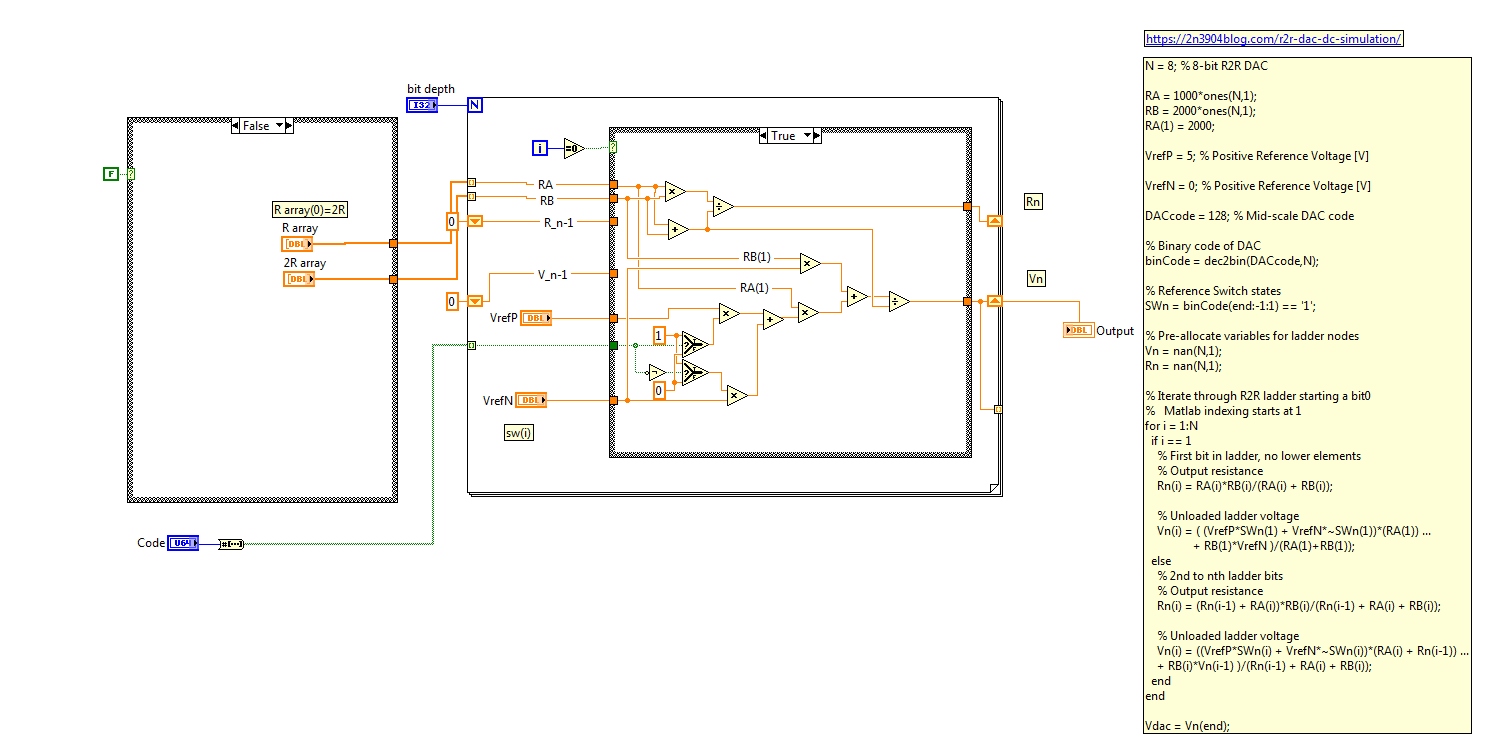

回頭講一下模擬程式本身, 因為 2N3904Blog 推導的式子已經十分詳細, 轉換成

LabVIEW code 以後驗算一下跟 SPICE 的數字吻合 (8-bit 用 0x55 =85 與

3.3-(-1)= 4.3V 的偏壓代入會得到 0.377923V 的輸出)就可以確認公式的正確性. 這

其實適合出給大一電機系的學生當作練習題, 差不多學過半個學期的電路學跟程式數值計

算就能做出來.

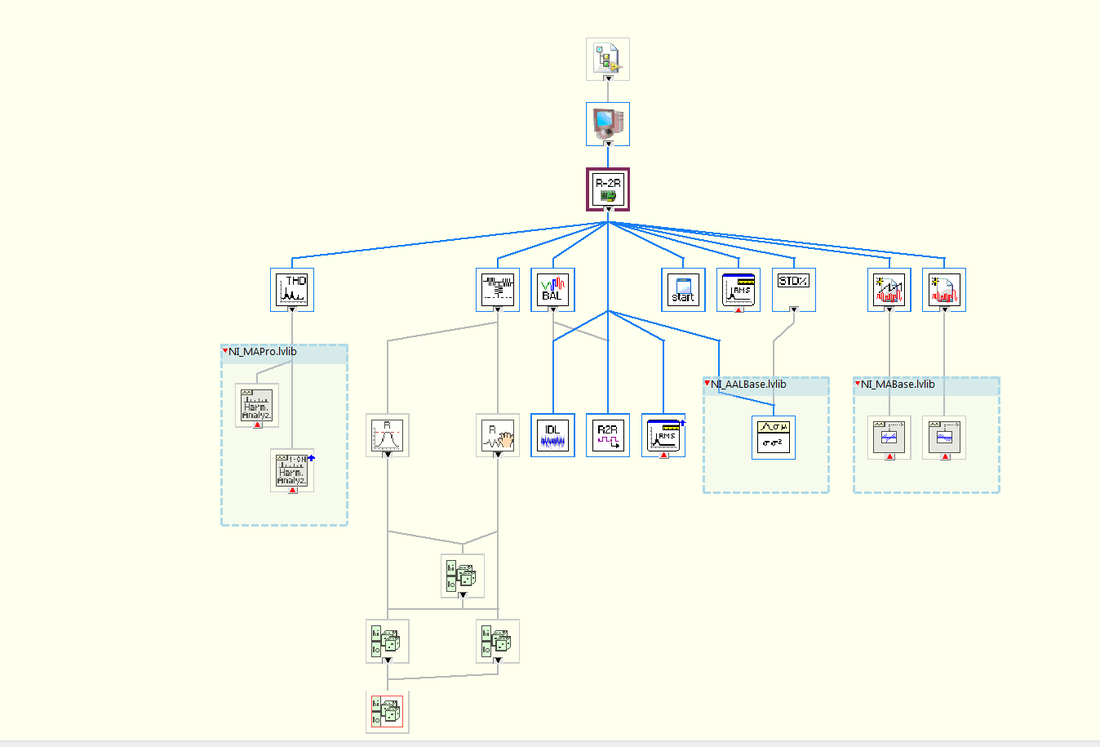

http://chihhanlin.weebly.com/uploads/8/4/4/0/8440048/code01_orig.png

以上就是整個模擬程式的核心, 靜態計算出 R-2R 在不同的 binary switch 開關狀態下

(DAC input code, 以 8-bit 來說就是 0x00, 0x01 一直到 0xFF 共 256 種可能的狀態

) 配合 n-階 R-2R ladder 後真正的類比電壓輸出值, 這個核心程式稍做修改甚至允許你

加入一些修正項, 比如說 Vref 的浮動(可以每個 bit 設定不同值)或者把開關的導通

阻抗也一併加入, 計算出正確的 transfer function 後也可以拿來模擬

Segmented-ladder 跟 Sign Magnitude/balance 架構. 假設響應無限快那麼只要帶入波

形的不同時刻的 input code 就可以得到對應的 R-2R 類比電壓輸出值, 換句話說只要再

寫個測試波形產生器, 電阻陣列亂數產生器以及簡單的頻譜分析程式就能觀察電阻精度匹

配對於諧波失真的影響, 這件事情在量產時電阻打件的時候很重要. 以前原本想用

SPICE 來做這件事情, 後來想想先用靜態等效電路模型去做雖然有些不足, 但是可以快

速取得一些值得參考的數據.

http://chihhanlin.weebly.com/uploads/8/4/4/0/8440048/code02_1_orig.png

簡單弄出幾個功能. 用 LabVIEW 寫的好處就是快, 隨便拉一拉結果就出來了 , 常用的

FFT 跟圖表呈現方式設定方便.

http://chihhanlin.weebly.com/uploads/8/4/4/0/8440048/code03_orig.png

程式架構十分簡單, 測試時個別區塊(波形產生器, 電阻陣列亂數產生器等等)寫好後包成

subVI,因為只有單次模擬跟連續模擬兩種狀態就用個 state machine 包起來, 透過

event structure 去做 UI 控制 (Event Driven State machine 的 design pattern,

一般來說會這個就有資格跟別人唬爛說會寫 LabVIEW 的儀控程式).

http://chihhanlin.weebly.com/uploads/8/4/4/0/8440048/code04_orig.png

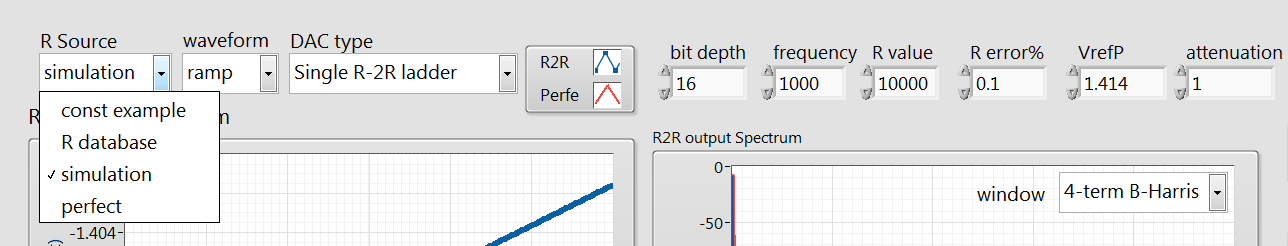

右邊的 bit depth 就是 R-2R ladder 模擬的位數, 從 1-63 bit 都可以 (當然還可以

更高, 不過 LabVIEW 預設的整數最大就 U64, 不想另外寫 function 就做了這個限制),

attenuation 則是可以改變模擬單頻訊號的不同振幅, 這個可以用來觀察小訊號時 THD

成份是否隨之有所變化. 選單上主要的模擬類型有三個項目, R Source, waveform 跟

DAC type. R source 當中有四個項目:

1. const example, 從 soekris DAM1121 上量下來的一組 0.01%/0.02% 電阻的實際量測

值, 可參考 Soekris OEM 解析

2. R database. 一樣是 soekris DAM1121 上量到的 52 顆 10K ohm 電阻值, 這個選項

可以從這個陣列隨機抽出 n 顆 R 與 n 顆 2R (R 直接乘以兩倍) 構成 R-2R ladder

3. simulation. 根據右邊參數列的 R value 跟 R error% 自動生成 R-2R 陣列, 電阻值

由 R value -0.5 R error% 到 R value + 0.5 R error% 均勻分佈

4. perfect. 完美的 R-2R ladder, 每個電阻值當剛好是 R value 跟 2R value, 圖表中

R2R output waveform 跟 spectrum 作為對照的紅線基準會跟這組參數吻合.

waveform 的部份則有 sine 跟 ramp 兩種, 顧名思義 sine 就是產生頻率為 frequency

的單頻訊號, 預設振幅 1.414 Volt (這樣頻譜基頻那根就是 0dB), 48KHz 取樣率以及

65536 點. ramp 則是 input code 從 0x00..00 線性掃描到 0xFF..FF 的鋸齒波, 如果

是 n-bit R-2R dac 就會生成 2^n 個資料點, 主要用來看 IDL. 由於 LabVIEW 對單一陣

列的記憶體限制我把 ramp 模式 bit depth 上限鎖在 16bit , 當然我自己的版本要模擬

到 20bit 以上都不是問題

最後 DAC type 的部份 Single R-2R ladder 就是最基本的單端 R-2R , balanced

(Sign Mag.) 就是目前各家 R-2R audio 大廠的唯一解, MSB Technology 及 Soekris 稱

為 Sign Magnitude dac , 亦或是末代王者 BB PCM1704 談到的 balanced dac , 兩者指

的是同樣的結構. 這種方式幾乎是解決過零失真的唯一解 (反正大家應該都是抄 MSB 的

, PCM1704 電流型以非晶圓製程來說離散電路不好搞所以沒人抄). 匪區 HIFIDIY 論壇

的 forsli 的文章中對於 balance DAC 的 input code 解碼有詳細的講解 (要注意這不

是像平衡訊號一樣一正一反兩個相減就可以, 那樣只是一般的 differential 而非

balanced ,必須將信號正半周與負半周分別交由兩個獨立 DAC 來解碼), 這個架構漂亮

地讓小訊號時只有 LSB 側的開關作動, 不需要補償 MSB 高位電阻值來消除過零失真, 唯

一的代價就是兩倍大的電阻陣列. 如果你有點慧根, 看了 US patent US5257027, A

Modified sign-magnitude DAC and method (本文一開始給的參考資料, 想當然耳是 BB

提出來的) 應該可以自己用 CPLD/FPGA 或 I/O 夠多的單晶片寫出對應的解碼器, 這個在

我四歲的時候就已經公開的專利現在早就過期了, 江湖一點訣, 說破就不值錢了.

https://youtu.be/U2Om2ZzgFd0

程式執行上非常簡單, Fetch 按鈕就是按照面板設定單次執行, Cont. Fetch 就是不斷重

複進行模擬, THD 資訊會成現在右上方面板, 不同次模擬得到的計算值會出現在右下方的

THD chart, 當然在 ramp 波形下看 Spectrum 跟 THD 就沒有太大意義. 連續模擬的過

程可以動態改變 waveform 與 bit depth 以外的各種參數.

以下列出一些模擬結果

電阻精度對於 INL 的影響

https://youtu.be/g5NksFgnjYQ

透過 ramp 模擬訊號我們可以觀察電阻精度匹配如何影響 DAC 輸出的線性度, 也就是

INL. 輸出結果有點像碎形, 最大的轉折點在1/2 Full range (MSB 的匹配), 再來是

1/4 跟 3/4 (MSB 跟第二位), 這是 binary weighting 的必然結果. 一般來說在 MSB

串聯加入一顆 offset 電阻的做法就是在修正 MSB 對於 INL 的影響, 不是最好的方式但

是對於大訊號輸出的時候已經相當有用. 使用 Segmented 的方式 (並聯 2^n-1 顆電阻來

達成 n-bit MSBs) 用 equal weighting 來取代 binary weighting 也是一種方式. 其

實 DNL (differential nonlinearity) 對於 dac 動態表現(隨時間變化的那個動態而不

是動態範圍)可能更加重要, 為了避免透露太多秘密這個就不放在教學性質的 demo 裡了.

0.01% 精度電阻陣列在不同 bit 數下 THD 的極限

https://youtu.be/SeilfHmhrdE

這個模擬結果固定使用 0.01% 精度的電阻 (標準差約 0.003%). 模擬由此種電阻構成的

R-2R 陣列依序由 12-bit, 13-bit 往上增加的 THD 變化. 我們最後會發現這樣的

R-2R ladder 到了 17-bit 左右 THD 就不會在更小, 0dBFS 大概在 0.001% 到

0.002% 之間 (100dB), 額外增加的 ladder 長度並不會有任何幫助, 換句話說 INL 的

量被電阻精度限制. 0.01% 也是市面上大多數 R-2R 廠家的極限, 就算選用更高精度的電

阻也會被開關的導通阻抗影響匹配 (很多菜用高速 shift register 的數位開關輸出阻抗

都 50 ohm +-40% 以上, 相較 10K ohm 的 R 值來說已經很大), 正常來說看到的頻譜諧

波失真的量在 -100dB 以下就算上得了檯面的產品.

壟斷分立/離散 audio R-2R 的 Sign Magnitude/Balanced DAC 架構

https://youtu.be/Ic6QQNtjKUA

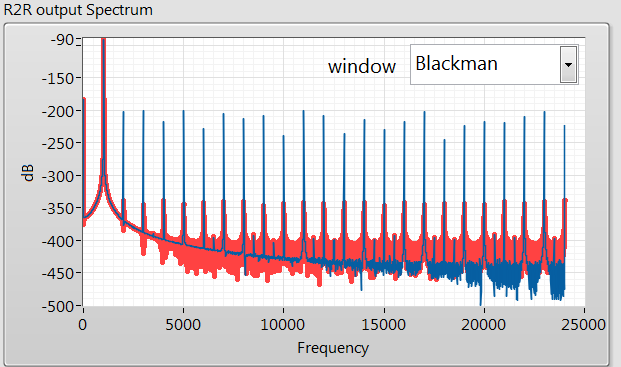

這個模擬結果充分展示了 Sign Magnitude / balanced dac 架構的優越程度. 在大訊號

的時候其實跟 differential 差不多, 就是 6dB 的提升, 但是一旦把輸入訊號的振幅降

到 0.01 (-20dB) 甚至是 0.001 (-60dB) 時馬上可以發現這個架構強大之處, 幾乎可以

確保小訊號的時候不會因為 MSB 位的電阻匹配而產生巨大的 THD (換句話說小訊號的

SFDR, Spurious Free Dynamic Range 表現有大幅提升), 增加 R-2R ladder 長度這件

事情在 Sign Magnitude / balanced dac 顯得非常有意義. 絕大多數的 R-2R DAC

DIYer 做出來的試作品小音量會有可聽見的嘶聲就是沒有理解處理過零失真的重要性, 只

有跨過這個坎才有上打廠機的基本資格 (雖然 99.9% 的都是用 Segmented balanced

dac 的結構來解決).

http://chihhanlin.weebly.com/uploads/8/4/4/0/8440048/data01_orig.png

這張數據呈現的結果很明顯 (輸入 1KHz -60dB), THD chart 左半部是 single R-2R,

THD error 從 0 - 2% 都可能發生, 如果 MSBs 的電阻值剛好接近平均值那出來的數字還

能看, 但實際狀況是半數以上的產品 THD 都會大於 1%, 一旦採用 balanced DAC 架構以

後 THD 立馬降到 0.006% 以下, 以同樣精度的電阻原料做出來的成品變異 (CV) 非常的

低, 這也是好的廠機上幾乎只會出現 Sign Magnitude / balanced 架構的緣故 (不過也

可能單純只是大家互抄)

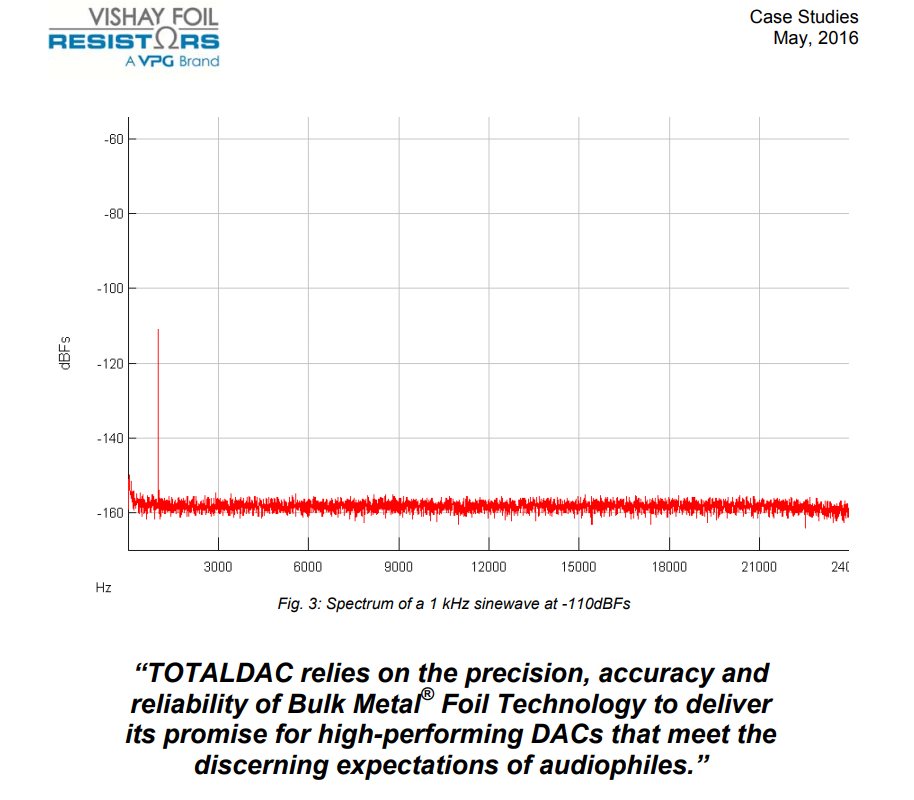

最後再補充一些實際產品的對照. 在 Vishay FOIL resistors 官方 case study (May

2016) 中也出現過 totaldac R-2R 產品的小訊號數據量測結果, 我的模擬程式也可以估

計出這樣條件中 THD 下限

http://chihhanlin.weebly.com/uploads/8/4/4/0/8440048/data02_orig.png

http://www.vishaypg.com/docs/63601/totaldac.pdf

http://chihhanlin.weebly.com/uploads/8/4/4/0/8440048/data03_orig.png

模擬的結果諧波失真的量都在 -160dB 以下

模擬因為沒有電源底噪所以 FFT 的 noise floor 都特別低, 不過推算出來的諧波失真還

是符合實際結果, 24-bit R-2R 採用正確架構控制好電阻精度在 -100dBFS 要讓 THD 被

noise floor 掩蓋並不是難事. 當然因為模擬程式動了點小手腳的關係所以得到的理論

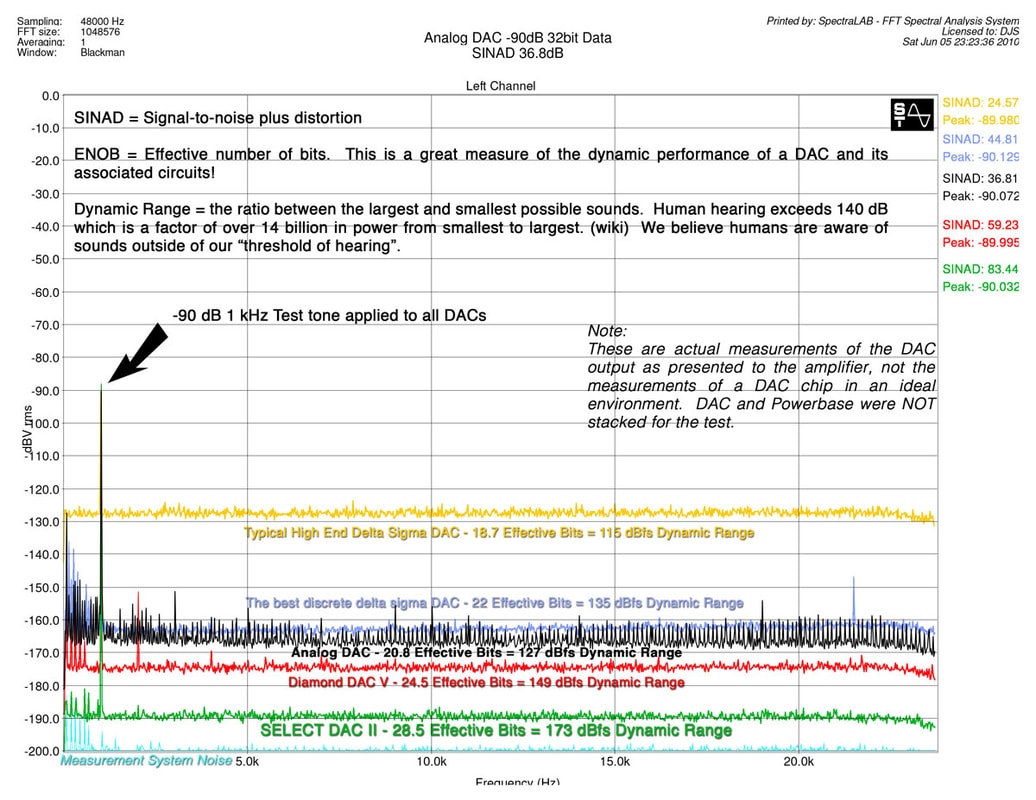

值有點偏大 (其實只是錯位故意沒疊好). 再來看 MSB Select DAC 那張囂張的 SINAD 數

據

http://chihhanlin.weebly.com/uploads/8/4/4/0/8440048/msb90db-graph_orig.jpg

用的是 48KHz -90dBFS, 32-bit 的 R-2R ladder 去模擬, 用的 FFT point 一樣是

1048576 points, Blackman window.

姑且不論那個匪夷所思的 -200dB noise floor 怎麼達成的, 用 0.01% 精度的電阻陣列

在 -90dBFS 做到極限是有可能讓 THD 低於 noise floor , 其實按照正常算法等校位數

ENOB 我覺得只能算 16-17bits , 就算用了 Sign Magnitude 的把戲也不太可能在

full range 的輸出下達到 173dB 的 dynamic range.

-----------後記-----------------

http://chihhanlin.weebly.com/uploads/8/4/4/0/8440048/krab_1_orig.jpg

上個月跑去看香格里拉內構的時候順便在巴城品嘗了正宗陽澄湖大閘蟹, 即便致癌超標還

是值得一吃啊. 下半年一下班就泡在健身房跟家裡的練習台玩 zwift 沒空寫雜文 , 今年

目標就是要蹲破 120kg 5rm , FTP 200W 跟弄出個可以聽的 R2R prototype 啊

--

※ 發信站: 批踢踢實業坊(ptt.cc), 來自: 59.120.61.247

※ 文章網址: https://www.ptt.cc/bbs/Headphone/M.1513683955.A.DFD.html

推

12/19 19:49,

6年前

, 1F

12/19 19:49, 1F

推

12/19 19:49,

6年前

, 2F

12/19 19:49, 2F

推

12/19 19:50,

6年前

, 3F

12/19 19:50, 3F

推

12/19 19:56,

6年前

, 4F

12/19 19:56, 4F

推

12/19 20:03,

6年前

, 5F

12/19 20:03, 5F

→

12/19 20:03,

6年前

, 6F

12/19 20:03, 6F

推

12/19 20:10,

6年前

, 7F

12/19 20:10, 7F

推

12/19 20:15,

6年前

, 8F

12/19 20:15, 8F

推

12/19 20:17,

6年前

, 9F

12/19 20:17, 9F

推

12/19 20:18,

6年前

, 10F

12/19 20:18, 10F

→

12/19 20:27,

6年前

, 11F

12/19 20:27, 11F

→

12/19 20:27,

6年前

, 12F

12/19 20:27, 12F

→

12/19 20:27,

6年前

, 13F

12/19 20:27, 13F

推

12/19 20:33,

6年前

, 14F

12/19 20:33, 14F

→

12/19 20:48,

6年前

, 15F

12/19 20:48, 15F

→

12/19 20:48,

6年前

, 16F

12/19 20:48, 16F

→

12/19 20:48,

6年前

, 17F

12/19 20:48, 17F

→

12/19 21:00,

6年前

, 18F

12/19 21:00, 18F

推

12/19 21:05,

6年前

, 19F

12/19 21:05, 19F

→

12/19 21:12,

6年前

, 20F

12/19 21:12, 20F

→

12/19 21:12,

6年前

, 21F

12/19 21:12, 21F

→

12/19 21:12,

6年前

, 22F

12/19 21:12, 22F

推

12/19 21:41,

6年前

, 23F

12/19 21:41, 23F

推

12/19 21:49,

6年前

, 24F

12/19 21:49, 24F

推

12/19 22:58,

6年前

, 25F

12/19 22:58, 25F

推

12/19 23:21,

6年前

, 26F

12/19 23:21, 26F

推

12/20 00:13,

6年前

, 27F

12/20 00:13, 27F

→

12/20 00:14,

6年前

, 28F

12/20 00:14, 28F

推

12/20 00:44,

6年前

, 29F

12/20 00:44, 29F

→

12/20 01:17,

6年前

, 30F

12/20 01:17, 30F

→

12/20 01:17,

6年前

, 31F

12/20 01:17, 31F

推

12/20 01:33,

6年前

, 32F

12/20 01:33, 32F

推

12/20 01:41,

6年前

, 33F

12/20 01:41, 33F

推

12/20 01:58,

6年前

, 34F

12/20 01:58, 34F

推

12/20 03:58,

6年前

, 35F

12/20 03:58, 35F

→

12/20 08:15,

6年前

, 36F

12/20 08:15, 36F

推

12/20 08:23,

6年前

, 37F

12/20 08:23, 37F

推

12/20 12:02,

6年前

, 38F

12/20 12:02, 38F

→

12/20 12:03,

6年前

, 39F

12/20 12:03, 39F

→

12/20 12:03,

6年前

, 40F

12/20 12:03, 40F

推

12/20 13:14,

6年前

, 41F

12/20 13:14, 41F

→

12/20 13:14,

6年前

, 42F

12/20 13:14, 42F

推

12/20 13:19,

6年前

, 43F

12/20 13:19, 43F

→

12/20 13:36,

6年前

, 44F

12/20 13:36, 44F

→

12/20 13:37,

6年前

, 45F

12/20 13:37, 45F

→

12/20 13:39,

6年前

, 46F

12/20 13:39, 46F

→

12/20 13:40,

6年前

, 47F

12/20 13:40, 47F

推

12/20 13:58,

6年前

, 48F

12/20 13:58, 48F

→

12/20 13:58,

6年前

, 49F

12/20 13:58, 49F

推

12/20 15:21,

6年前

, 50F

12/20 15:21, 50F

推

12/20 16:22,

6年前

, 51F

12/20 16:22, 51F

推

12/21 01:02,

6年前

, 52F

12/21 01:02, 52F

推

12/22 12:56,

6年前

, 53F

12/22 12:56, 53F