[問題] 單級放大器也會有LHP zero嗎?

會問這個主要是最近在做V-to-I電路

https://imgur.com/Wg4XDBh

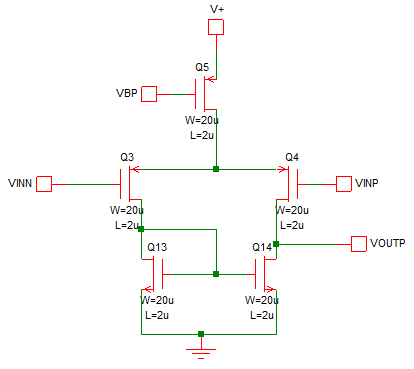

放大器採單級 輸入對因為input range較低採用PMOS(下圖size非實際選用大小)

https://www.analogictips.com/wp-content/uploads/2017/05/opampspumped-image1.png

看AC時 當小訊號從放大器負端斷開輸入

如果看OP內部Q13的GD相連該線

會發現有個左半平面的zero出現(如下圖標示位置 上為Gain下為Phase)

https://imgur.com/39klhEY

想請教大家的是 這是有可能的嗎?

後來發現這個zero位置跟Q3以及Q4的size大小有關(在設計的時候他們的Wf跟L都很大)

但就算是跟CGD有關係 在沒加nulling電阻情況下他應該產生的是右半平面的zero吧?

怎麼會產生左半平面出來了?

再次感謝各位了!!!

--

※ 發信站: 批踢踢實業坊(ptt.cc), 來自: 106.1.235.210 (臺灣)

※ 文章網址: https://www.ptt.cc/bbs/Electronics/M.1646070069.A.4BC.html

推

03/01 02:53,

2年前

, 1F

03/01 02:53, 1F

→

03/01 02:56,

2年前

, 2F

03/01 02:56, 2F

→

03/01 11:28,

2年前

, 3F

03/01 11:28, 3F

→

03/01 11:33,

2年前

, 4F

03/01 11:33, 4F

→

03/01 11:39,

2年前

, 5F

03/01 11:39, 5F

不好意思真的弄錯了囧

已經換上正確的圖和敘述

推

03/01 11:41,

2年前

, 6F

03/01 11:41, 6F

→

03/01 11:41,

2年前

, 7F

03/01 11:41, 7F

→

03/01 11:41,

2年前

, 8F

03/01 11:41, 8F

→

03/01 11:42,

2年前

, 9F

03/01 11:42, 9F

→

03/01 11:44,

2年前

, 10F

03/01 11:44, 10F

→

03/01 11:44,

2年前

, 11F

03/01 11:44, 11F

→

03/01 11:48,

2年前

, 12F

03/01 11:48, 12F

不好意思看不太懂 input pair不算是一種cs嗎?

另外能請教一下5 mos ota的pole2跟zero位置在哪嗎

很多只寫到單一極點由CL決定就結束了...(還是pole2就是我說Q13的G D端?)

※ 編輯: WetDreamZZZ (106.1.235.210 臺灣), 03/01/2022 23:58:06

→

03/02 10:19,

2年前

, 13F

03/02 10:19, 13F

→

03/02 10:20,

2年前

, 14F

03/02 10:20, 14F

→

03/02 11:03,

2年前

, 15F

03/02 11:03, 15F

→

03/02 11:03,

2年前

, 16F

03/02 11:03, 16F

→

03/02 11:04,

2年前

, 17F

03/02 11:04, 17F

→

03/02 11:06,

2年前

, 18F

03/02 11:06, 18F

→

03/02 11:07,

2年前

, 19F

03/02 11:07, 19F

→

03/02 11:11,

2年前

, 20F

03/02 11:11, 20F

→

03/02 11:15,

2年前

, 21F

03/02 11:15, 21F

→

03/02 11:15,

2年前

, 22F

03/02 11:15, 22F

→

03/02 11:15,

2年前

, 23F

03/02 11:15, 23F

→

03/02 11:15,

2年前

, 24F

03/02 11:15, 24F